9월초 공개될 것으로 예상되는 인텔 아이태니엄 프로세서의 차세대 모델 '폴슨'의 세부 스팩이 공개됐다.

이달 중순 인텔은 아이태니엄 프로세서 9500 시리즈(코드명:폴슨) 레퍼런스 매뉴얼을 공개했다. 유닉스용 칩인 인텔 아이태니엄 프로세서의 최신 모델 9500 시리즈는 9550, 9520, 9540, 9560 등 4종으로 출시된다.

이번에 공개된 매뉴얼은 소프트웨어 개발 최적화를 위한 용도다. 매뉴얼은 HP 논스톱, 오픈VMS, HP-UX 시스템에서 작동하는 코드 사용법을 소개하고 있다. 아이태니엄 프로세서는 HP의 유닉스 서버에 가장 많이 사용되며, 불(BULL), 후지쯔, NEC 등이 일부 모델에 채택하고 있다.

폴슨에 대한 정보는 작년 2월 솔리드 스테이트 서킷 컨퍼런스에 앞서 공개됐다. 지난해까지 알려진 폴슨은 32나노미터 공정으로 생산되고, 프로세서 당 8개의 코어를 갖는다. 프로세서엔 31억개의 트랜지스터가 집적됐다.

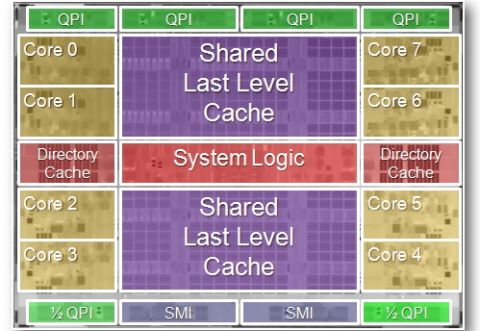

2개의 디렉토리 캐시, 5개의 퀵 패스 인터커넥트(QPI) 링크, 두개의 SMI DDR3 메모리 컨트롤러(소켓당 512GB), 두 개의 공유 L2 캐시, 단일 시스템 로직 등으로 구성된다.

코어당 소비전력은 170와트이며, 이는 185와트였던 투퀼라(아이태니엄 9300)에서 더 개선된 것이다. CPU 클럭수는 9550 2.4GHz, 9520 1.73GHz, 9540 2.13GHz, 9560 2.53GHz 등이다. 투퀼라는 1.33GHz~1.73GHz 수준이었다. 전력 제어기술의 개선으로 코어수와 클럭수를 함께 늘릴 수 있었다.

폴슨은 54MB의 SRAM 메모리를 갖게 된다. 32MB의 코어당 4MB씩 8개 블록으로 나뉜 L3 캐시를 보유하며, L2 데이터캐시는 총 2MB다. 전체 L2 인스트럭션 캐시는 4MB이며, 디렉토리 캐시가 2.2MB다. 3.6MB의 최후 레벨 태그와 169KB의 L2 인스트럭션 태그를 지원한다.

인텔은 신뢰성(reliability), 가용성(availability), 보수 용이성(serviceability) 등에 대한 RAS 기능이 강화된 게 주된 특징이라고 밝히고 있다.

각 코어는 16KB의 L1 데이터캐시, L1 인스트럭션 캐시를 갖는다. 모든 캐시는 오류 데이터를 찾아내어 수정하는 ECC 메모리를 갖는다.

프로세서의 중앙엔 10포트의 크로스바 라우터가 자리한다. 이 라우터는 칩 상에서의 메모리와 I/O 교환을 관리한다. 칩 아래쪽에 절반의 QPI 링크 2개가 자리한다. 상단 QPI링크가 4개 있어 전체적으로 5개의 QPI를 갖는다.

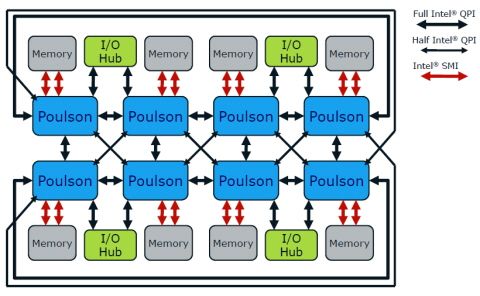

이 QPI 링크들은 다른 CPU 칩셋과 연결해 SMP나 NUMA 프로세싱 지원을 확장할 수 있다.

절반 크기의 QPI 링크는 초당 3.2기가 트랜잭션(GTps)의 대역폭을 보인다. 9300시리즈의 전체 QPI 포트 대역폭인 4.8GTps보다 뛰어나다. 완전한 QPI링크는 6.4GTps를 지원한다. 전체 SMI메모리의 대역폭은 초당 45기가바이트를 처리하지만, QPI를 사용하면 초당 128기가바이트를 처리할 수 있다.

폴슨은 멀티 스레딩 모델을 개선했다. 이와 함께 하이퍼 스레딩 기술로 듀얼 도메인 멀티 스레딩을 지원한다.

관련기사

- CPU보다 I/O를 주목해야 하는 이유2012.07.27

- 마지막 차세대 유닉스 전쟁, 8월 열린다2012.07.27

- HP, 고뇌의 2010년 '유닉스 출구전략'2012.07.27

- '인텔 아이태니엄 CPU의 종말'…진실은?2012.07.27

폴슨은 코어당 8천900만개의 트랜지스터를 갖고 있는데, 투퀼라 코어가 1억900만개였다. 더 작은 공간에 더 적은 트랜지스터를 사용하고도 성능을 높인 것이다. 투퀼라에 비해 전체 프로세싱속도는 30.1~46.2% 가량 향상됐다.

폴슨 프로세서는 9월 중 출시될 것으로 보인다. 인텔은 9월초 미국 샌프란시스코에서 인텔 개발자 포럼을 개최하는데, 이곳이 폴슨의 공개장소가 될 것으로 예상된다.