세계 최대 파운드리 업체인 대만 TSMC가 칩을 수직으로 쌓아 올리는 형태의 일명 ‘3D칩’ 기술을 개발, 올 연말 상용화할 예정이다.

TSMC는 이를 통해 지난 5월 초 인텔이 개발한 3D칩과 경쟁하겠다는 것이다. 그러나 이 회사가 말하는 3D는 인텔과 전혀 다른 방식인 것으로 알려졌다.

EE타임즈·일렉트로닉스위클리닷컴 등 주요 외신은 5일(현지시간) 대만무역센터(TAITRA)의 보고서를 인용, “TSMC는 일명 ‘3D칩’이라고 불리는 이 기술로 지난 5월초 인텔에서 공개한 22나노미터(nm) 공정을 사용한 ‘3D칩’ 기술과 경쟁하겠다는 뜻을 밝혔다”고 보도했다.

그러나 이들 보도는 정확하게 말하면 TSMC가 3D기술로 부르는 것은 인텔과 같은 수준으로 보기는 힘들다.

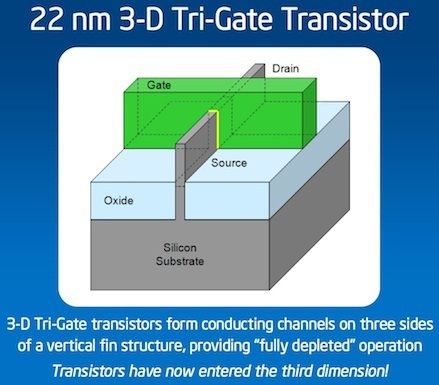

TSMC가 발표한 것은 ‘3D인터커넥트’ 기술로 수십 마이크로미터(㎛) 두께로 만든 칩에 구멍을 뚫은 뒤 이들을 수직으로 쌓아올려 구멍에 전기가 통하는 물질을 넣어 연결하는 ‘관통전극(Through Silicon via)’이라는 패키징 방식이다. 하지만 지난 5월 인텔이 발표한 것은 ‘트라이게이트’라 불리는 기술로 평면형 트랜지스터를 입체형으로 만든 것이다. 실리콘을 핀(Fin)이라고 하는 얇은 지느러미 모양으로 세우고 그 양면에 전자가 흐르는 게이트를 설치하는 이중 게이트 구조를 가진다. 마치 1차선 도로에 고가도로를 지은 것처럼 두 배 이상의 전류가 흐를 수 있도록 했다.

관련기사

- 차세대 메모리 적층기술 전쟁 스타트2011.07.06

- 인텔 52년만의 반도체혁명···3D칩 등장2011.07.06

- [이재구코너]인텔 4004 탄생2011.07.06

- 삼성부터 현대까지 국내 기업, 앞다퉈 '생성형AI' 영접하다2024.05.05

인텔이 이 기술을 발표한 다음날 나온 보도에 따르면 TSMC는 ‘트라이게이트’ 기술이 안정화될 때까지 이 분야에 진출할 생각은 없다고 밝힌 바 있다. TSMC가 말한 3D칩은 기존에 메모리 제조업체들이 사용하고 있는 최신공정이기는 하나 인텔과 같은 기술은 아니라는 설명이 된다.

TSMC는 단일 칩에서 기존 트랜지스터 집적 방식보다 1천배 이상 많은 트랜지스터를 집적할 수 있으며, 전력소비량을 절반으로 낮출 것으로 예상했다. 인텔은 기존 반도체에 비해 성능을 37% 높이고 전력소모량을 절반 이상 줄일 수 있다고 밝힌 바 있다.