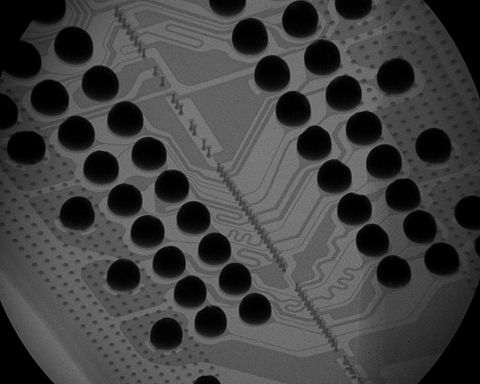

하이닉스반도체(대표 김종갑)는 7일 업계 최초로 관통 전극(TSV) 기술을 활용해 웨이퍼 레벨 패키지(WLP)를 2단으로 적층하는 기술을 개발했다고 밝혔다.

웨이퍼 레벨 패키지 기술이란 웨이퍼 가공 후 하나씩 칩을 잘라내 패키징하던 기존 방식과 달리, 웨이퍼 상태에서 한 번에 패키지 공정 및 테스트를 진행한 후 칩을 절단해 완제품을 만들어 내는 기술이다.

하이닉스반도체에 따르면 이번에 개발된 기술은 웨이퍼 레벨 패키지에 관통전극 기술을 적용, 칩을 2단으로 적층한 것이다. 때문에 데이터 전송 경로가 짧아지면서도 더 많은 정보입출구(I/O)를 만들 수 있어 고성능 패키지 구현이 가능하게 되었다는 것. 패키지 크기와 두께를 줄이면서 비용이 낮아져 제조원가도 절감될 전망이다

변광유 패키지 개발 그룹장은 “이번 개발은 웨이퍼 레벨 패키지와 관통전극 기술의 장점만을 취한 패키지 형태”라며 “향후 4단, 8단 이상의 적층까지 개발할 것”이라고 말했다.

관련기사

- 하이닉스 신임 CEO 권오철 전무 내정2010.03.07

- 하이닉스, 설 연휴 맞아 봉사활동2010.03.07

- ‘꼼짝마!’…AI 접목 금융 이상거래 탐지 ‘한 끗’ 차별화2024.05.01

- "더 늦으면 큰일"…생성형 AI로 기업 체질 어떻게 바꿀까2024.05.02