“2단계의 장애물을 모두 뛰어 넘었다. ”

IBM이 상변화메모리와 차세대데이터 스토리지 문제를 모두 해결한 차차세대 메모리를 내놨다. 이 메모리는 오는 2016년 서버용으로 사용될 것이라고 발표했다.

씨넷은 29일(현지시간) IBM연구진이 드리프트(drift)기술을 이용해 2비트의 데이터를 각 상변화메모리(Phase Change Memory PCM)셀에 넣는데 성공한 사실을 발표했다고 보도했다. 또 이를 최근 국제전기전자엔지니어협회(IEEE)가 개최한 IEEE국제메모리워크숍에서 논문을 통해 발표했다고 전했다.

보도는 비록 이것이 멀티레벨셀이라고 불리는 이 아이디어를 처음으로 구현한 것으로 아니지만 연구원들은 자신들이 ‘드리프트’라는 방식을 사용해 이를 처음으로 실용화할 수 있었다고 말했다고 전했다.

■드리프트 이용해 데이터 에러 문제 해결

IBM연구원들은 드리프트가 이전까지는 좀 더 긴 데이터가 저장할 경우 데이터에러를 일으키는 문제점들을 우회하는 방법이었다고 밝혔다.

기술적 발전은 지금까지 가능성으로만 인식되던 엄청난 기술소개의 장벽을 극복해 이를 컴퓨터설계의 엄청난 변화로 이끌도록 해주고 있다.

상변화메모리는 전통적인 D램에 달라붙어 지금까지 플래시메모리가 할 수 없었던 컴퓨터 성능향상 기능을 제공한다.

이 보고서 공저자인 해리스 포지디스 IBM연구원은 “IBM의 상변화메모리기술은 당장 현실적으로 사용할 수 있는 것은 아니다. 하지만 멀티레벨 저장 및 드리프트 토러런스는 이 기술이 오는 2016년쯤이면 IBM이 생각하고 있는 서버기술에 사용할 수 있을 정도의 경쟁력을 가지게 될 전망이다.

포지디스는 “서버분야가 될 우리의 주된 애플리케이션은 엔터프라이즈 스토리지와 메모리 애플리케이션”이라고 말했다.

그는 “소비자시장에서 가장 중요한 특징은 비트당 가격이다. 하지만 엔터프라이즈 애플리케이션에서는 상변화메모리가 초당 많은 트랜잭션이 발생하는 메인메모리에 가까이 있게 될 것이기 때문에 가장 중요한 특징은 메모리 속도와 디바이스의 내구성”이라고 말했다. 그는 “우리는 이 디바이스가 여러 번 읽고 쓸 수 있도록 확실하게 만들어야 한다”고 말했다.

■휴대폰에서는 PCM기술 조기 상용화 가능성

IBM은 상변화기술을 가진 유일한 업체가 아니다. 삼성전자,하이닉스,마이크론 등도 이 상변화 메모리 기술을 가지고 있다. 26년전에 메모리 생산을 중단한 인텔도 이 기술을 연구하고 있다. 또한 학계의 많은 연구원들도 이에 도전하고 있다.

최근의 사례를 보면 스탠포드 연구진이 카본 나노튜브를 이용해 PCM셀을 더욱더 컴팩트하게 만든 사례가 보고되고 있고 샌디에이고대에서는 오닉스(Onyx)로 불리는 10GB의 상변화메모리(PCM)스토리지를 만든 바 있다.

포지디스는 “IBM은 상변화메모리를 만들 계획을 가지고 있지 않지만 이 기술을 다른 반도체 제조업체에 라이선싱할 계획”이라고 말했다.

서버급 PCM은 오는 2016년에 시장에 등장할 계획이다. 하지만 다른 시장은 또다른 수요를 가지면서 더 빠른 시장 움직임을 보일 것으로 전망됐다.

예를 들면 삼성은 휴대폰에 노어(NOR)방식의 플래시메모리를 대체할 칩으로 PCM칩을 팔 전망이다.

PCM은 인텔의 고든 무어 공동창업자가 1970년대에 자신의 논문에서 언급한 적이 있을 정도로 등장한 지가 매우 오래된 기술이다.

당시 인텔은 이 기술을 소개하기 위해 오보닉스(Ovonics)라는 단어를 사용했지만 P램, PC램, 그리고 칼코겐(상변화 메모리의 중심물질)화합물 램 등이 있었다.

■기존 플래시 SSD의 단점을 보완

그러나 강력한 네트워크 기반의 컴퓨터인 서버의 경우 웹사이트 호스트로서 이메일교환, 및 재무관련 거래가 발생하고 있어 대체할 수 있는 거대한 시장으로 인식되고 있다.

플래시메모리는 하드디스크드라이브의 성능을 엄청나게 향상시켜주는 솔드스테이트디스크(SDD)라는 형태로 서버시장을 공략해 오고 있다.

하지만 플래시SSD는 비쌀 뿐만 아니라 데이터를 읽고 쓰면서 시간이 지나면 지날 수록 품질이 떨어진다는 단점이 지적돼 오고 있다.

플래시메모리 컨트롤러는 데이터를 새로운 플래시메모리로 옮김으로써 이 문제를 우회적으로 해결하고 있다.

IBM측은 “플래시메모리는 비즈니스급 스토리지 제품의 경우 3만회의 쓰기 사이클, 일반 가전 제품용 플래시메모리는 3천번의 쓰기 사이클이 지나면 품질이 떨어지기 시각한다”고 말했다.

IBM은 “이에 비해 PCM은 적어도 1천만 번의 읽고 쓰기를 수행할 수 있다”고 말했다.

포지디스는 PCM이 데이터 읽고 쓰기를 더욱 빠르게 수행하는 디램을 대체할 것이라고 예상하지 않고 있다.

그러나 PCM은 데이터를 다시 끌어올 경우 빠른 접속을 위한 데이터 캐싱을 통해 D램 성능을 끌어올 릴 수 있다.

■차차세대 메모리의 작동원리는?

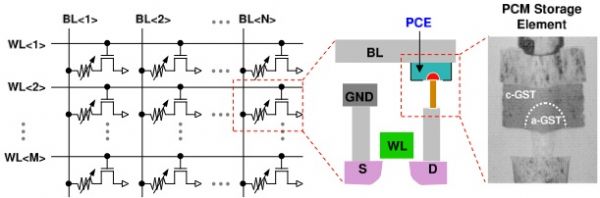

상변화메모리는 데이터를 저장하기 위한 단순한 기본 디자인을 가지고 있다. 즉 열이 작은 유리질의 칼코겐(Calcogenide)물질의 전기속성을 변화시키는 것이다.

이 반도체가 급속히 냉각되면 반도체 물질이 뜨거울 때의 비정질 형태로 뒤죽박죽된 상태를 유지하게 된다. 하지만 상대적으로 천천히 냉각될 경우엔 분자가 수정체 격자형태로 나란히 배열하게 돼 전기를 훨씬더 잘 전달하게 해준다. 이 전기저항을 측정함으로써 이 디바이스는 셀이 얼마나 데이터를 저장하는지를 알아낸다. 그리고 제어된 방식으로 이를 가열하고 냉각함으로써 새로운 데이터가 쓰여지는 원리다.

멀티레이어(다층)접근 방식을 통해 이 셀은 4개의 서로 다른 결정과 비정질 상태로 만들어져 사용된다. 4개의 상태(state)에서 2비트로 표현되는 데이터, 즉 00,01,10, 그리고 11이라는 2진법 형태의 데이터가 각 셀에 저장된다. 이 방식은 메모리칩의 밀도를 2배로 만들고 주어진 데이터를 저장하는 비용을 줄여준다.

하지만 이것으로도 충분치 않다. 오늘날의 플래시 메모리는 셀당 3비트의 데이터가 저장될 수 있음을 의미하는 8개의 상태(state)를 사용하기 때문이다.

포지디스는 “우리는 PCM이 그수준으로 가야 하며, 할 수 있다고 믿는다“고 강조했다.

그는 “사실 가능성 있는 다른 물질을 사용하면 PCM에 셀당 4비트를 담을 수 있게 될 것”이라고 말했다.

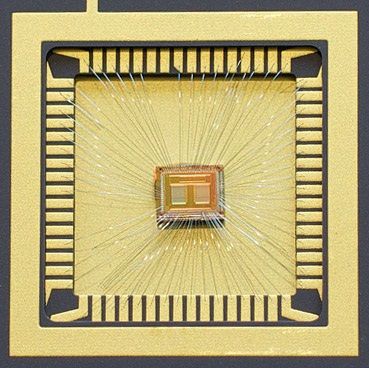

IBM은 자사의 멀티레벨셀 기술을 2억5600만셀을 가진 칩에서 시연했다.

셀당 2비트의 데이터를 저장함으로써 이 능력은 512메가비트가 됐다.

포지디스는 “드리프트 톨러런트기술은 더 작은 2메가셀버전에서 사용됐다”고 말했다.

이 두 기술은 보다 오래된 90나노생산공정세서 만들어졌다.

포지디스는 “PCM을 가격경쟁력있게 만드는 핵심은 이를 현대적 제조공정으로 줄이는 것”이라고 말했다. 즉 오늘날 플래시 메모리 회로선폭인 24나노급 공정으로 만드는 것이라는 설명이다.

그는 “상변화는 훨씬더 낮은 디멘전으로 낮출 수 있다”고 말했다.

■IBM의 해법은

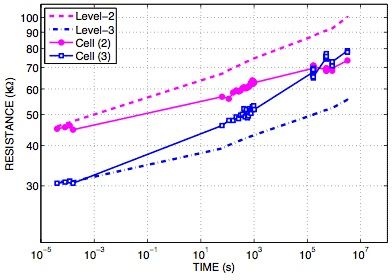

PCM의 문제 가운데 하나는 시간이 지남에 따라 데이터를 기록하는 전기저항레벨이 표류한다는 점이다. 이 그래프는 2개 메모리셀의 드리프트를 보여준다. 각 셀은 4개 저항레벨을 가진 데이터를 저장할 수 있다. 서로 다른 상변화메모리의 저항레벨 간의 차이가 정밀해져 갈수록 저항표류(resistance drift)라고 불리는 문제가 더 빨리 발생하게 된다.

드리프트가 발생하면 특정 셀의 저항도 시간의 경과에 따라 변화해 서로다른 레벨 간의 경계를 모호하게 만들며, 데이터 오염까지 가져오게 된다. 서로 다른 셀이 서로다른 비율로 표류하기 때문에 이를 다루기란 쉽지 않다.

이 문제를 해결하기 위해 IBM이 택한 접근방식은 일부 셀에 실제 데이터대신 IBM이 코드워드(codeword)라고 부르는 것을 기록하도록 하는 것이었다.

변조코딩(Modulaton coding)으로 불리는 이 방식은 IBM으로 하여금 셀의 절대적인 전기저항자체가 아닌 상대적인 속성을 측정할 수 있게 해주고 있다.

포지디스는 “우리는 분자 입력방식(coding)을 설계했으며 따라서 이는 우리가 변화할 것으로 알고 있는 절대 저항 수준에서 정보를 저장하는 것이 아니라 상대적인 순서에 따라 정보를 저장하도록 한 것”이라고 말했다.

그 결과 이 기술을 실용화할 수 있도록 에러율을 크게 낮췄다.

관련기사

- 차세대 메모리 적층기술 전쟁 스타트2011.07.01

- 인텔, 차세대 메모리 현실화 '눈앞'2011.07.01

- 차세대 메모리 피램, 특허 출원 '활발'2011.07.01

- 삼성전자, 뉴모닉스와 차세대 메모리 기술 협력2011.07.01

이 논문은 “표류를 견디는 이른 바 드리프트 톨러런트(drift toleralent)코딩이 실내온도(보통 섭씨18도)에서 37일이 지나도 10만개 메모리셀 가운데 1의 에러가 발생할 정도의 에러율을 보인 것은 상당히 인상적”이라고 쓰고 있다.

또 “단순하고 낮은 중복 에러정정 코드(low-redundancy error-correction codes)는 실질적인 메모리디바이스를 만드는데 요구되는 전반적인 에러율을 1천조 분의 1 정도, 또는 그 이하로 떨어뜨리는데 충분했다”고 쓰고 있다.